2019年的top500超算中,速度最快的美国summit超算性能达到了20亿亿次,第二名的中国神威·太湖之光性能超过10亿亿次,不过一两年之后10亿亿次级别的性能将被新一代超算超越,人类将会进入百亿亿次超算时代。

intel就为美国能源部承建了极光(aurora)超算,它将使用intel的xeon处理器、新一代xe加速卡、傲腾dc持久内存以及one api软件。极光超算运算性能超过百亿亿次,是现有最强超算的10-20倍,实现了指数级增长。

新一代超算之所以如此大幅度提升性能,是因为人类未来几年所需要的计算性能需求增长太快了,2025年全球产生的数据量高达175eb,智能互联的设备高达1500亿,完全是一个数据洪流时代,更快地传输数据、存储更多数据以及处理一切是硬要求。

为了应对未来的数据中心时代,intel去年提出了六大技术支柱的战略,包括制程与封装、架构、内存与存储、互连、安全、软件。intel认为计算需求无处不在,而且日益多样化,cmos缩放、3d工艺技术、新架构、新功能等将继续推动摩尔定律向前发展,但是任何单一因素都不可能再满足多元化的未来计算需求,而基于六大技术支柱的指数级创新,将是intel进入未来10年乃至下一个50年的驱动力。

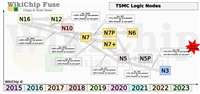

在intel的六大支柱技术中,先进的制程工艺及封装技术是基础,其中先进工艺方面intel已经有14nm工艺及改进工艺,今年又量产了10nm工艺,之后还会有改进版10nm+及10nm++工艺,2021年则会量产7nm工艺,针对5nm、3nm的研究也在进行中。

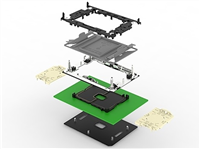

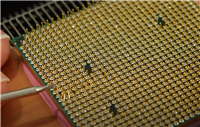

与以往的不同的是,芯片封装技术的重要性首次被提升到与制程工艺相提并论的程度,之前业界谈摩尔定律都是指同一支撑下的单芯片,其发展已经受到了光罩的限制,而在未来的数据中心时代,产品不再受制于光光罩,它可以集成多种针对ip优化多制程小芯片,这也是业界刚开始流行的chiplet设计思路。

chiplet小芯片的设计很容易让人联想到之前的胶水多核,看起来都是把不同的芯片封装在组合成一个芯片,但二者实际有本质区别——胶水多核只是简单的2d多芯封装,而chiplet复杂得多,是3d封装技术,不同的芯片有不同的架构甚至制程工艺,这种异构集成技术提供了前所未有的灵活性,有助于解决传统2d芯片性能无法大规模扩展、功耗过高等难题。

在先进封装技术上,intel走的也很快,之前已经有emib 2.5d封装技术,去年底又率先推出了foveros 3d封装技术,有望首次将晶片的堆叠从传统的无源中间互连层和堆叠存储芯片扩展到高性能逻辑芯片,如 cpu、图形和人工智能处理器。

前几天的semicon west大会上,intel又推出了三项全新的先进芯片封装技术,并推出了一系列全新基础工具,包括emib、foveros技术相结合的创新应用,新的全方位互连(odi)技术等。

·co-emib:利用利用高密度的互连技术,将emib(嵌入式多芯片互连桥接) 2d封装和foveros 3d封装技术结合在一起,实现高带宽、低功耗,以及相当有竞争力的i/o密度。

co-emib能连接更高的计算性能和能力,让两个或多个foveros元件互连从而基本达到soc性能,还能以非常高的带宽和非常低的功耗连接模拟器、内存和其他模块。

·odi:odi全称omni-directional interconnect,也就是全方位互连技术,为封装中小芯片之间的全方位互连通信提供了更大的灵活性。odi封装架构中,顶部的芯片可以像emib下一样,与其他小芯片进行水平通信,还可以像foveros下一样,通过硅通孔(tsv)与下面的底部裸片进行垂直通信。

·mdi:基于高级接口总线(aib)物理层互连技术,intel发布了这种名为mdio的全新裸片间接口技术。mdio技术支持对小芯片ip模块库的模块化系统设计,能效更高,响应速度和带宽密度可以是aib技术的两倍以上。

intel将从今年开始应用上述先进封装方式,首先是lakefield处理器上集成10nm cpu及22nm io核心,而基于co-emib的芯片也有了样品,在一块基板上都有多达9个裸片(die),且大小、功能各异,整合方式也不一样。

到了2020年,intel的3d封装技术会在各个领域前面开花。

在今后的发展中,硅基半导体依然会受摩尔定律的指导,10nm、7nm及未来的5nm、3nm工艺依然会带来晶体管微缩、性能提升,提高以数据为中心时代的计算性能。

但是另一方面,先进工艺制造难度越来越大,也使得成本大幅上涨,开发7nm芯片需要3亿美元的费用,是10nm工艺的2倍左右,5nm节点甚至会增长到5.4亿美元,这也让半导体公司担心用不起。

这也是intel为何在六大支柱技术中将封装技术与工艺并列的原因,单纯依赖工艺带来的性能增长已经无法实现指数级增长,无法满足数据洪流时代的计算要求,而foveros、co-emib、odi、mdi等3d封装技术具备更高的灵活性,一方面可以继续集成高性能工艺及先进架构核心,另一方面也可以集成其他工艺、架构的io核心等,能够让intel对架构、制程和封装同时进行优化,从而交付领先的产品。

如对本文有疑问, 点击进行留言回复!!

2年升级一次 Intel:10nm、7nm及5nm工艺开发不会削减投资

AMD推土机FX-8350超频至8.1GHz!却打不过3.6GHz锐龙

网友评论