半导体行业的技术难度正呈几何指数般的速度加大,以往很多惯用手段都开始渐渐失灵了。面对越来越难做的芯片,未来该何去何从?

最近,intel提出了革命性的foveros 3d立体芯片封装技术,首次为cpu处理器引入了3d堆叠式设计,堪称产品创新的催化剂,或将成为cpu处理器历史上一个重要的转折点。

它允许在新的设备外形中“混搭”(mix and match) 不同工艺、架构、用途的技术 ip 模块、各种内存和 i/o 元件,使得产品能够分解成更小的组合,同时将之前分散、独立的不同模块结合为一体,以满足不同应用、功耗范围、外形尺寸的设计需求,以更低的成本实现更高的或者更适宜的性能。

其实在此之前,intel曾经应用过一种2d集成技术“emib”(嵌入式多芯片互连桥接),把不同工艺、功能的ip模块整合到单一封装中,相比传统2d单片设计更有利于提高良品率、提升整体性能、降低成本、加快产品上市速度,典型产品代表就是集成了intel八代酷睿cpu、amd vega gpu图形核心的kaby lake-g系列。

foveros则进化到了3d集成,延续2d集成各种优势的同时,加上全新水平的集成密度和灵活性,首次让逻辑芯片可以堆叠在一起,彻底颠覆并重新构建了系统芯片架构。

套用刘慈欣科幻大作《三体》里的一个流行梗,可以说intel站在3d的角度上,对传统2d芯片发动了一场“降维打击”。

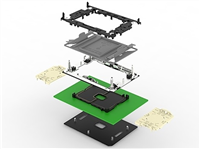

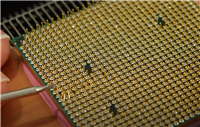

在intel提供的foveros 3d堆叠封装示意图上,可以清楚地看到这种盖楼式设计的巧妙之处:

最底部的封装基板之上,是核心的基础计算芯片,再往上可以堆叠计算、视觉等各种模块,高性能逻辑、低功耗逻辑、高密度内存、高速内存、传感器、功率调节器、无线电、光电子等等就看你需要什么了,无论是intel ip还是第三方ip都可以和谐共处,客户完全可以根据需要自由定制。

这是从侧视角度展示的foveros 3d封装的结构示意图:最下边是封装基底,之上安放一个底层芯片(bottom chip),起到主动中介层(active interposer)的作用——amd fiji/vega核心整合封装hbm显存就有类似的存在。

中介层之上就可以放置各种不同的新品或模块,比如cpu、gpu、内存、基带……

而在中介层里有大量的tsv 3d硅穿孔,负责联通上下的焊料凸起(solder bump),让上层芯片和模块与系统其他部分通信。

当然,如何处理不同模块之间的高速互连,确保整体性能、功耗等都处于最佳水平,无疑是非常考验设计能力和技术实力的,tsv硅穿孔、分立式集成电路就是其中的关键所在。

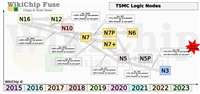

intel表示,不同用途芯片或者功能模块对晶体管密度的需求是截然不同的,性能、功耗、成本也相差很大,因此所有芯片模块都使用同一种工艺不会达到最佳效果,尤其是新工艺越来越难,都硬上新工艺不值得,也越来越不容易做到。

intel还强调,3d封装不一定会降低成本,但重点也不在于成本,而是如何把最合适的ip放在最合适的位置上,进行混搭,这才是真正的驱动力。

foveros 3d封装技术将从2019年下半年开始,陆续出现在一系列产品中,未来也会成为intel芯片设计的重要根基。

首款产品代号为“lakefield”,也是全球第一款混合cpu架构产品。intel同时展示了基于该处理器的小型参考主板,称其可以灵活地满足oem各种创新的设备外形设计。

lakefield将会结合高性能的10nm运算堆叠小芯片、低功耗的22nm ffl基础硅片,首次展示的参考设计示例中,就集成了cpu处理器、gpu核心显卡、内存控制器、图像处理单元、显示引擎,以及各种各样的i/o输入输出、调试和控制模块。

作为混合x86架构产品,它拥有一个10nm工艺的高性能sunny cove cpu核心(ice lake处理器就用它),以及四个10nm工艺的低功耗atom cpu核心,二者既有自己的独立缓存,也共享末级缓存,同时核芯显卡也和ice lake一样进化到第11代,不但有多达64个执行单元,功耗也控制得非常低。

除了规格设计上的先进,更让人激动和期待的是它的超小体积和超低功耗。

这颗小芯片的长宽尺寸只有12×12毫米,高度仅仅1毫米,还没一枚硬币大,但内部3d堆叠封装了多个模块。

基底之上是p1222 22ffl(22nm工一种)工艺的io芯片,低成本、低漏电。

之上是p1274 10nm工艺计算芯片,也就是传统cpu,内部整合了一个sunny core高性能核心、四个atom低功耗核心(或许是tremont新架构)。

再往上甚至还有pop整合封装的内存芯片。

intel宣称,它的待机功耗只有区区2mw,也就是0.002w,最高功耗也不超过7w,很显然是针对移动平台的,而且不需要风扇,可用于11寸以下便携式小型设备。

芯片设计从2d平铺转向3d堆叠,这就为设备和系统结合使用高性能、高密度和低功耗芯片制程技术奠定了坚实的基础,也为半导体行业的发展和突破打开了一扇新的大门,有了更多的新思路可以探索。

foveros 3d封装技术的提出,充分说明intel已经找准了未来芯片设计的新方向,不再拘泥于传统框架,可以更加灵活地设计性能更强、功能更丰富、功耗更低、用途更灵活的不同产品,满足差异化设备和市场需求。

如对本文有疑问, 点击进行留言回复!!

2年升级一次 Intel:10nm、7nm及5nm工艺开发不会削减投资

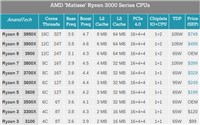

AMD推土机FX-8350超频至8.1GHz!却打不过3.6GHz锐龙

网友评论