ieee iedm大会上,台积电官方披露了5nm工艺的最新进展,给出了大量确凿数据,看起来十分的欢欣鼓舞。

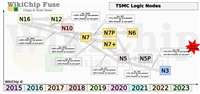

5nm将是台积电的又一个重要工艺节点,分为n5、n5p两个版本,前者相比于n7 7nm工艺性能提升15%、功耗降低30%,后者在前者基础上继续性能提升7%、功耗降低15%。

台积电5nm将使用第五代finfet晶体管技术,euv极紫外光刻技术也扩展到10多个光刻层,整体晶体管密度提升84%——7nm是每平方毫米9627万个晶体管,5nm就将是每平方毫米1.771亿个晶体管。

台积电称5nm工艺目前正处于风险试产阶段,测试芯片的良品率平均已达80%,最高可超过90%,不过这些芯片都相对很简单,如果放在复杂的移动和桌面芯片上,良品率还做不到这么高,但具体数据未公开。

具体来说,台积电5nm工艺的测试芯片有两种,一是256mb sram,单元面积包括25000平方纳米的高电流版本、21000平方纳米的高密度版本,后者号称是迄今最小的,总面积5.376平方毫米。

二是综合了sram、cpu/gpu逻辑单元、io单元的,面积占比分别为30%、60%、10%,总面积估计大约17.92平方毫米。

按照这个面积计算,一块300mm晶圆应该能生产出3252颗芯片,良品率80%,那么完好的芯片至少是2602个,缺陷率1.271个每平方厘米。

当然,现代高性能芯片面积都相当大,比如麒麟990 5g达到了113.31平方毫米。

按照一颗芯片100平方毫米计算,1.271个每平方厘米的缺陷意味着良品率为32%,看着不高但对于风险试产阶段的工艺来说还是完全合格的,足够合作伙伴进行早期测试与评估。

另外,amd zen2架构每颗芯片(八核心)的面积约为10.35×7.37=76.28平方毫米,对应良品率就是41%。

台积电还公布了5nm工艺下cpu、gpu芯片的电压、频率对应关系,cpu通过测试的最低值是0.7v、1.5ghz,最高可以做到1.2v 3.25ghz,gpu则是最低0.65v 0.66ghz、最高1.2v 1.43ghz。当然这都是初步结果,后续肯定还会大大提升。

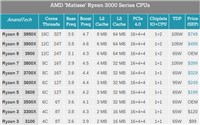

台积电预计,5nm工艺将在2020年上半年投入大规模量产,相关芯片产品将在2020年晚些时候陆续登场,苹果a14、华为麒麟1000系列、amd zen4架构四代锐龙都是妥妥的了,只是

如对本文有疑问, 点击进行留言回复!!

2年升级一次 Intel:10nm、7nm及5nm工艺开发不会削减投资

AMD推土机FX-8350超频至8.1GHz!却打不过3.6GHz锐龙

网友评论