在本周旧金山举办的semicon west大会上,intel介绍了三项全新的先进芯片封装技术,并推出了一系列全新基础工具,包括emib、foveros技术相结合的创新应用,新的全方位互连(odi)技术等。

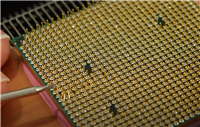

作为芯片制造过程的最后一步,封装在电子供应链中看似不起眼,却一直发挥着极为关键的作用。作为处理器和主板之间的物理接口,封装为芯片的电信号和电源提供着陆,尤其随着行业的进步和变化,先进封装的作用越来越凸显。

另一方面,半导体工艺和芯片架构的日益复杂,传统soc二维单芯片思路已经逐渐行不通,chiplet多个小芯片封装成为大势所趋。

intel正是利用先进技术,将芯片和小芯片封装在一起,达到soc的性能,而异构集成技术提供了前所未有的灵活性,能够混搭各种ip和工艺、不同的内存和i/o单元,intel的垂直集成结构在异构集成时代尤其独具优势。

intel此次公布的三项全新封装技术分别是:

一、co-emib

利用利用高密度的互连技术,将emib(嵌入式多芯片互连桥接) 2d封装和foveros 3d封装技术结合在一起,实现高带宽、低功耗,以及相当有竞争力的i/o密度。

co-emib能连接更高的计算性能和能力,让两个或多个foveros元件互连从而基本达到soc性能,还能以非常高的带宽和非常低的功耗连接模拟器、内存和其他模块。

foveros 3d封装是intel在今年初的ces上提出的全新技术,首次为cpu处理器引入3d堆叠设计,可以实现芯片上堆叠芯片,而且能整合不同工艺、结构、用途的芯片,相关产品将从2019年下半年开始陆续推出。

二、odi

odi全程omni-directional interconnect,也就是全方位互连技术,为封装中小芯片之间的全方位互连通信提供了更大的灵活性。

odi封装架构中,顶部的芯片可以像emib下一样,与其他小芯片进行水平通信,还可以像foveros下一样,通过硅通孔(tsv)与下面的底部裸片进行垂直通信。

odi利用更大的垂直通孔,直接从封装基板向顶部裸片供电,比传统硅通孔更大、电阻更低,因而可提供更稳定的电力传输,同时通过堆叠实现更高的带宽和更低的时延。

此外,这种方法减少了基底芯片所需的硅通孔数量,为有源晶体管释放更多的面积,并优化了裸片的尺寸。

三、mdio

基于高级接口总线(aib)物理层互连技术,intel发布了这种名为mdio的全新裸片间接口技术。

mdio技术支持对小芯片ip模块库的模块化系统设计,能效更高,响应速度和带宽密度可以是aib技术的两倍以上。

intel强调,这些全新封装技术将与intel的制程工艺相结合,成为芯片架构师的创意调色板,自由设计创新产品。

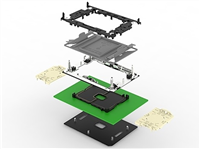

foveros封装流程图解:

odi封装主要特性图解:

如对本文有疑问, 点击进行留言回复!!

2年升级一次 Intel:10nm、7nm及5nm工艺开发不会削减投资

AMD推土机FX-8350超频至8.1GHz!却打不过3.6GHz锐龙

网友评论